Laporan Akhir 1

1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

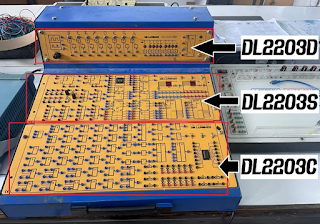

1. Panel DL 2203C.

2. Panel DL 2203D.

3. Panel DL 2203S.

4. Jumper.

4. Prinsip Kerja Rangkaian [Kembali]

Pada sasat clock berlogika 1 maka input clock pada rangkaian akan aktif (aktif high), yang mana akan merubah output sehingga yang merupakan output berlogika 1 adalah Q bukan Qnot lagi dan pada masukan D tidak aktif karna dihubungkan pada Qnot yang mana Qnot berlogika 0, sehingga Q berlogika satu dan Led merah menyala, kondisi ini menyatakan output dalam bilangan biner yaitu 0001, yang mana merupakan bilangan biner dari 1.

video penjelasan rangkaian percobaan 1

6. Analisa [Kembali]

1. Analisa sinyal output yang dikeluarkan masing-masing T flip flop? kenapa T flip terakhir disebut MSB?

pada T flip flop dimana inputan clocknya itu dihubungkan ke output dari TFlip Flop pertama sehingga masing-masing Tflip flop akan terjadi perubahan jika terjadi perubahan output pada Tflip flop pertama dari 1 ke 0.

flip flop pertama disebut MSB, bukan karna signifikasinya dalam representasi bilangan.

2. Analisa kondisi faltime dan risetime pada clock terhadap output pada percobaan yang dilakukan?

ketika clock mengalami percobaan output dan menghasilkan logika 1 dimana untuk bilangan biner di H0,H1,H2,H3 pertama yaitu 0000 dan diakhir 1000 yang dimana diakhir mengalami perubahan

.png)

Tidak ada komentar:

Posting Komentar